With the advent of AI and hyperscale designs on advanced nodes, it is common to see designs in over 50 billion transistor categories with tens to 100 billion plus nodes in the on-chip power network. This explosion in scale requires solutions that meet the following requirements:

◉ High performance and capacity.

◉ Elasticity.

◉ Manage varying compute resource requirements.

◉ Low cost to manage the exponential increase in compute requirements.

Voltus on Azure

Voltus is a leading IC Power Integrity Signoff Solution from Cadence Design Systems. It is used by top chip design companies to verify the reliability of their power networks on chip (NoC) and enables power integrity and thermal analysis at the system level.

Microsoft Azure provides a cloud-based high-performance computing (HPC) infrastructure with security, reliability, and scalability that is a natural fit for electronic design automation (EDA) workloads, especially power integrity analysis.

Azure can support both a hybrid model as well as an all-in model. In the hybrid model customers mainly use their on-premises infrastructure but can add to their compute and storage capacity on an on-demand basis to satisfy peak demand. The hybrid approach is typically used by customers new to using the cloud. In an all-in model, customers primarily use Azure infrastructure for all their EDA workloads. The all-in model is a great use case for startups and customers who really want to optimize their costs while taking advantage of the scale and flexibility of Azure. Voltus supports both the hybrid as well as the all-in model with Azure.

Managing variable compute costs through the design cycle

Using Azure can help customers optimize their costs as compute requirements will vary through the design cycle with lower requirements early on and peak demand near signoff. This is in contrast to the high fixed cost of on-premises infrastructure.

Running Voltus on Azure

We have used a block and full Chip test case to demonstrate our results.

The Azure team selected Edsv4 virtual machines (VMs) based on second-generation Intel Xeon Platinum 8272CL (Cascade Lake). These VMs are well suited for both compute and memory-intensive workloads.

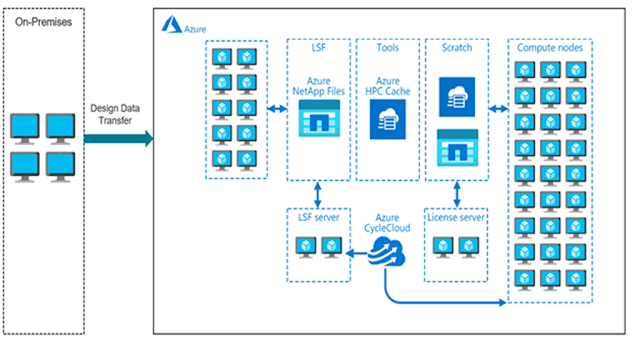

The Voltus use case setup on Azure is illustrated in Figure 1.

Figure 1

High performance and elasticity

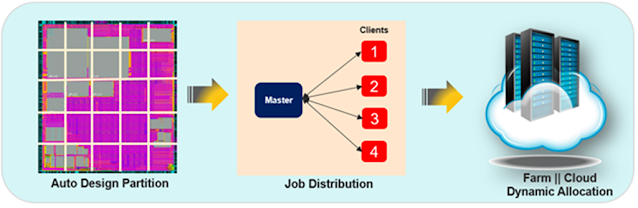

Voltus has a fully distributed and scalable architecture. Every step of the power integrity analysis flow, from design parsing to the solver, is fully distributed and scalable. Data from each part of the automatically partitioned design is assigned to compute nodes on the compute infrastructure for various steps in the analysis. This process is managed by a master machine as illustrated in Figure 2.

Figure 2

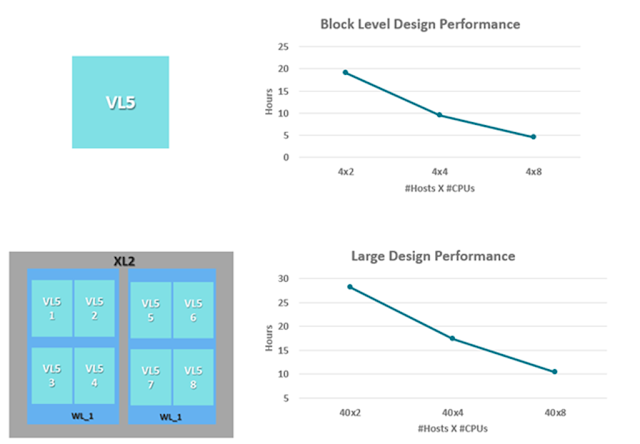

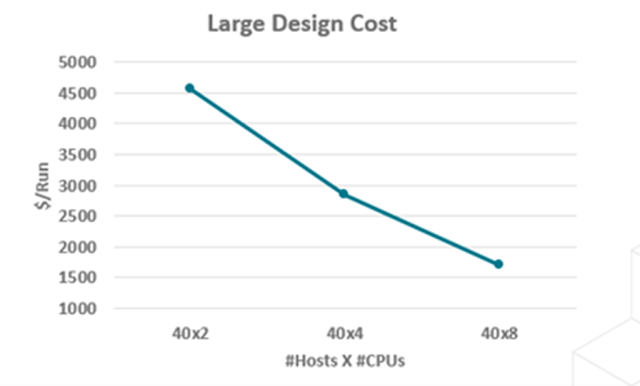

The level of distribution is user-controlled, which allows the user to take advantage of compute elasticity and manage performance. As Figure 3 illustrates for both the block and full chip run, we observe near-linear scalability in performance with respect to the number of CPUs.

Figure 3

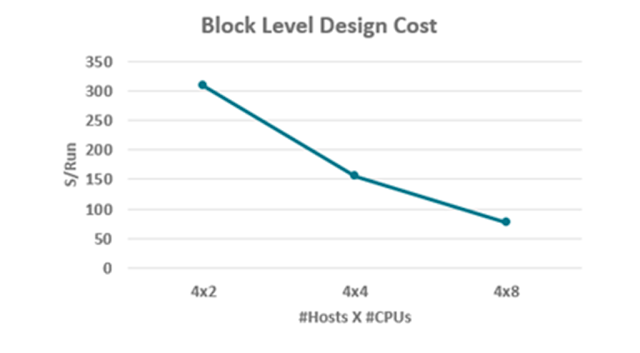

Higher performance with lower costs

Believe it or not, that is indeed true. The elasticity of Voltus architecture enables the tool to run faster with a higher number of CPUs and since the CPUs are used for a smaller amount of time, the result is that the total cost drops to an optimal point. This can be seen at both the block and full chip levels as illustrated in Figure 3. This is a win-win situation where you can improve your performance and reduce your costs.

Figure 4

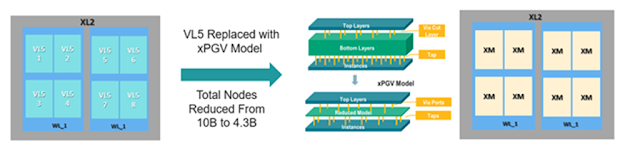

The magic of Voltus hierarchical analysis

Designers can further increase their performance and reduce cost by using Voltus XM hierarchical analysis. With Voltus XM, block-level models can be used instead of the full flattened design as illustrated in Figure 5. This method significantly reduces node count while maintaining accuracy. We can even further reduce our runtime and costs with Voltus XM and Azure. We observe a 4.5x reduction in cost and a 2x improvement in performance over the flat run for the full chip test case (Figure 6).

Figure 5

Figure 6

We have demonstrated the benefit of using Voltus on Azure at both the block level and chip level. These benchmarks show that customers can not only just benefit from higher performance using elastic compute, but there is an optimal point for performance and cost. Using Voltus XM hierarchical analysis further improves cost and performance. With Voltus on Azure, semiconductor companies have the ideal solution to verify power integrity for their most complex designs.

Source: microsoft.com

0 comments:

Post a Comment